19+ Fifo Depth Calculation

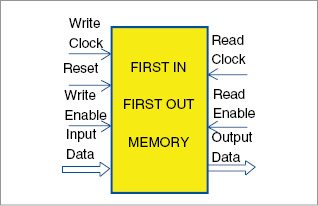

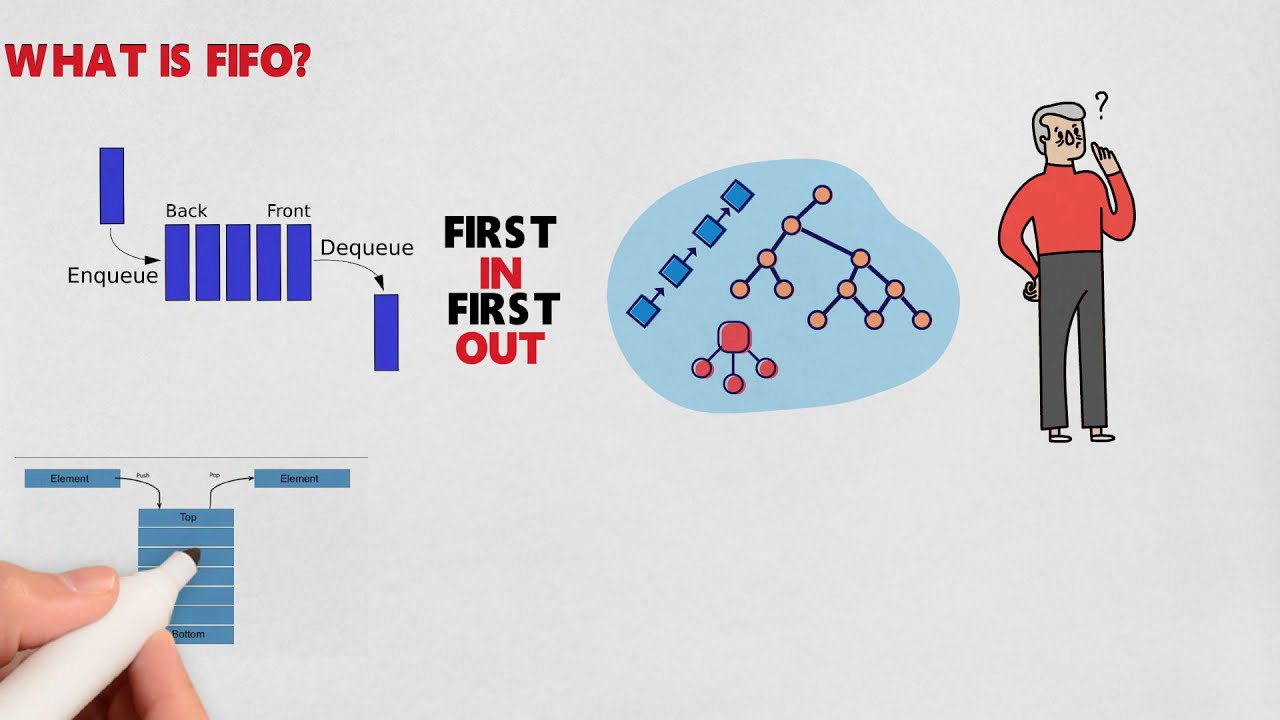

Hello Everyone In this Video I have explained how to calculate FIFO Depth. How to calculate Async Fifo Depth.

Fifo Depth Calculation Vlsi Vlsi Universe

Input is a 16 bit parallel data at 500MHz Output is 1 bit serial data at 50 MHz I need to.

. FIFO depth calculation and basics of clock domain crossing are touched in this tutorial. D B - clk_rdclk_wrB1RD Where D Depth or number of locations in FIFO to store. Formula to calculate FIFO depth below.

In the above example the cost of 250 units had. COGS FIFO 5000 5000 5 0 0 0. Hi All I have a design issue I have an interface between two domains.

This page contains tidbits on writing FSM in verilog difference between blocking and non blocking assignments in verilog difference between wire and reg metastability cross frequency domain. FIFO Depth calculation is one of the most commonly asked Interview question. Assuming you are continously reading and writing on both sides.

The fifo parameters are as follows. Consider F1 is writing frequency and F2 is reading frequency F1F2 and Data Size is D Data Words Time taken to write to. Contribute to sin-xFPGA development by creating an account on GitHub.

May 8 2014 at 1253 PM. For a theoretical perfect FIFO just solve the equation. The input source provides 66 bits of data at every clock of 1 Mhz.

This video provides a logical way to go through one of the most comm. Cost of Goods Sold FIFO 2000 3000 2000 3000 2 0 0 0 3 0 0 0. Fifo depth calculations Hi bharat_in sorry I misinterpreted the problem my understanding was 810 is write ratio and 80100 is read ratio.

Output to be provided is 40 bits every clock of 165 Mhz. A design requires a rate machine FIFO. Hi I want to calculate depth of an async fifo but I am confused how to calculate it.

Another Type of depth calculation can be done by this method. B Burst Width number of words to store before idle.

Fifo Computing And Electronics Wikipedia

Fifo Depth Calculation Part 3 By Technical Bytes Facebook

Serverless Noise Page 2

How To Create A Ring Buffer Fifo In Vhdl Vhdlwhiz

Solutions Manual Pdf

Inventory Valuation Fifo W Cogs Calculator Efinancialmodels

Deepfifo Explained How It Works Xillybus Com

How Do You Calculate Fifo Depth For Asynchronous Clock Having Same Frequency Forum For Electronics

Fifo Design Using Verilog Detailed Project Available

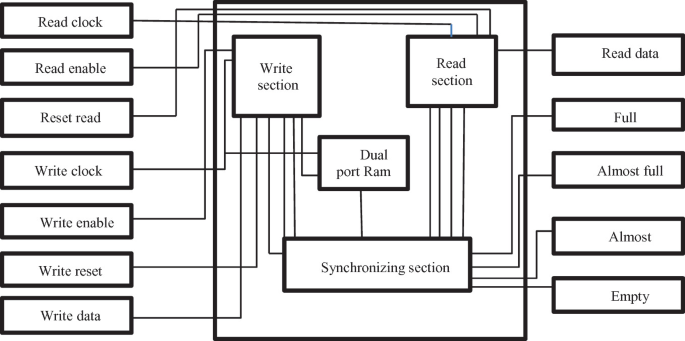

Fpga Implementation Of Asynchronous Fifo Springerlink

Fifo Buffer Module With Watermarks Verilog And Vhdl Logic Engineering And Component Solution Forum Techforum Digi Key

What Is Fifo Synchronous Fifo Asynchronous Fifo

3 Surprising Facts About Aws Sqs Fifo Queues Tom Gregory

Dual Clock Asynchronous Fifo In Systemverilog Verilog Pro

.png)

Plc Programming Understanding And Using Fifo S In Studio 5000

Verilog Fifo Block Implementation Stack Overflow

![]()

Formula For Depth Calculation For Any Fifo Syncronous Or Asyncronous Forum For Electronics